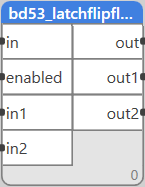

Latch flip-flop

Block name

BD53_LATCHFLIPFLOPNODE

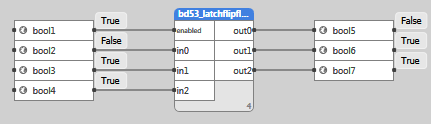

ST call

PROGRAM TEST_BD53 VAR BOOL1, BOOL2, BOOL3, BOOL4, BOOL5, BOOL6, BOOL7: BOOL; FB : LIB.CORE.V1_0.BD53_LATCHFLIPFLOPNODE; END_VAR FB.IN[1]:=BOOL2; FB.IN[2]:=BOOL3; FB.IN[3]:=BOOL4; FB(ENABLED:=BOOL1); BOOL5 := FB.OUT[1]; BOOL6 := FB.OUT[2]; BOOL7 := FB.OUT[3]; END_PROGRAM

Library

LIB\CORE

Version

V1.0

Description

The block is a gate for logical signals.

Inputs

| Input | Type | Description | Default value |

| ENABLE | BOOL | If enable=true then out0=in0,… | False |

| IN0,IN1,..,IN15 | BOOL | Inputs, individually | |

| IN | MULTIIOBOOL | Inputs array | [False] |

Outputs

| Output | Type | Description |

| OUT | MULTIIOBOOL | Outputs array |

| OUT0,OUT1,..,OUT15 | BOOL | Outputs, individually |

Function

The block is a gate: if enable=true then all inputs are copied to outputs. If enable=false the outputs keep the last value. Note that the ST indeces range is 1 to 16 rather than 0…15.