Table of Contents

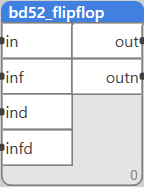

Flip-flop

Block name

BD52_FLIPFLOP

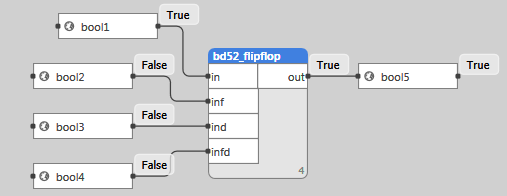

ST call

PROGRAM TESTST VAR BOOL1, BOOL2, BOOL3, BOOL4, BOOL5 : BOOL; FB : LIB.CORE.V1_0.BD52_FLIPFLOP; END_VAR FB(IN:=BOOL1, INF:=BOOL2, IND:=BOOL3, INFD:=BOOL4, OUT=>BOOL5); END_PROGRAM

Library

LIB\CORE

Version

V1.0

Description

The block controls its output value based on inputs, which read rising or falling edge, and thus set or reset the output.

Inputs

| Input | Type | Description | Default value |

|---|---|---|---|

| IN | BOOL | Rising edge sets out=true | False |

| INF | BOOL | Falling edge sets out=true | False |

| IND | BOOL | Rising edge sets out=false | False |

| INFD | BOOL | Falling edge sets out=false | False |

Outputs

| Output | Type | Description |

|---|---|---|

| OUT | BOOL | Output value |

| OUTN | BOOL | Negation of the output value |

Function

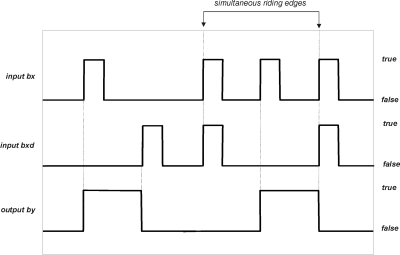

The block is a simple logical memory. Any rising edge at in and any falling edge at inf sets out=true. Any rising edge at ind and any falling edge at infd sets out=false. With more edges at the same time, out=false is preferred, see figure below. The output outn is negated out signal.

BD52 Flip-flop circuit – to keep it simple, inf=infd=false. Note that if more edges come at the same time, out=false is prioritized.