Table of Contents

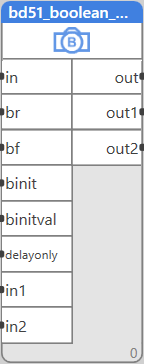

Boolean memory

Block name

BD51_BOOLEAN_MEMORY

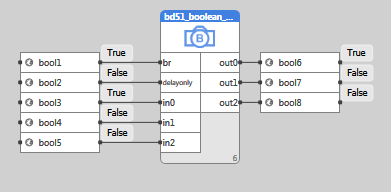

ST call

PROGRAM TEST BD51 VAR BOOL1, BOOL2, BOOL3, BOOL4, BOOL5, BOOL6, BOOL7, BOOL8: BOOL; FB : LIB.CORE.V1_0.BD51_BOOLEAN_MEMORY; END_VAR FB.IN[1]:=BOOL3; FB.IN[2]:=BOOL4; FB.IN[3]:=BOOL5; FB(BR:= BOOL1,DELAYONLY:=BOOL2); BOOL6 := FB.OUT[1]; BOOL7 := FB.OUT[2]; BOOL8 := FB.OUT[3]; END_PROGRAM

Library

LIB\CORE

Version

V1.0

Description

The block is a single-cycle signal delay block, or a boolean signal memory cell.

Inputs

| Input | Type | Description | False |

| IN | MULTIIOBOOL | Input array | [False,…,False] |

| BR | BOOL | Control by a rising edge | False |

| BF | BOOL | Control by a falling edge | False |

| BINIT | BOOL | Initialisation; if binit = false then out = binitval | True |

| BINITVAL | BOOL | Initial value to be set by binit | False |

| DELAYONLY | BOOL | Function of the block | False |

| IN0..IN15 | BOOL | Inputs individually as boolean variables |

Outputs

| Output | Type | Description |

| OUT | MULTIIOBOOL | Output array |

| OUT0..OUT15 | BOOL | Outputs individually as boolean variables |

Function

If the delayonly input is true, the block delays the input signal by one program cycle. If delayonly= false, the block is controlled by signals br and bf. Rising edge at br copies the inputs to the outputs. Similarly, falling edge at bf copies inputs to outputs. If binit = false, the output is set to binitval. If binit = true, the outputs are not initialised. Inputs may be connected either as multireal to in or separately to in0,in1,…. Note that the indeces in ST are 1…16 rather than 0…15.